| Name         |         |    |

|--------------|---------|----|

| Roll No.     | Year 20 | 20 |

| Exam Seat No |         |    |

**ELECTRONICS GROUP | SEMESTER - III | DIPLOMA IN ENGINEERING AND TECHNOLOGY**

# A LABORATORY MANUAL

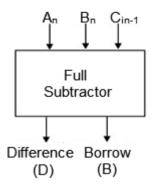

# DIGITAL TECHNIQUES (22320)

MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION, MUMBAI (Autonomous) (ISO 9001 : 2015) (ISO / IEC 27001 : 2013)

#### **VISION**

To ensure that the Diploma level Technical Education constantly matches the latest requirements of technology and industry and includes the all-round personal development of students including social concerns and to become globally competitive, technology led organization.

#### MISSION

To provide high quality technical and managerial manpower, information and consultancy services to the industry and community to enable the industry and community to face the changing technological and environmental challenges.

#### **QUALITY POLICY**

We, at MSBTE are committed to offer the best in class academic services to the students and institutes to enhance the delight of industry and society. This will be achieved through continual improvement in management practices adopted in the process of curriculum design, development, implementation, evaluation and monitoring system along with adequate faculty development programmes.

#### CORE VALUES

MSBTE believes in the followings:

- Education industry produces live products.

- Market requirements do not wait for curriculum changes.

- Question paper is the reflector of academic standards of educational organization.

- Well designed curriculum needs effective implementation too.

- Competency based curriculum is the backbone of need based program.

- Technical skills do need support of life skills.

- Best teachers are the national assets.

- Effective teaching learning process is impossible without learning resources.

#### **A Laboratory Manual**

for

# **Digital Techniques**

(22320)

#### **Semester-III**

(DE/EJ/ET/EN/EX/EQ/IE/IS/IC/MU/CO/CM/CW)

## Maharashtra State Board of Technical Education, Mumbai

(Autonomous) (ISO:9001:2015) (ISO/IEC 27001:2013)

# MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION

#### Certificate

| Roll No.        | r. / Ms<br>, of Third Semes                          | ter of Diploma in of Institute, |

|-----------------|------------------------------------------------------|---------------------------------|

| (Code:) has     | completed the term work  O) for the academic year 20 | satisfactorily in course        |

| Place:  Date:   | Enrollment No: Exam. Seat No:                        |                                 |

| Subject Teacher | Head of the Department  Seal of Institution          | Principal                       |

#### **Preface**

The primary focus of any engineering laboratory/ field work in the technical education system is to develop the much needed industry relevant competencies and skills. With this in view, MSBTE embarked on this innovative 'I' Scheme curricula for engineering diploma programmes with outcome-base education as the focus and accordingly, relatively large amount of time is allotted for the practical work. This displays the great importance of laboratory work making each teacher; instructor and student to realize that every minute of the laboratory time need to be effectively utilized to develop these outcomes, rather than doing other mundane activities. Therefore, for the successful implementation of this outcome-based curriculum, every practical has been designed to serve as a 'vehicle' to develop this industry identified competency in every student. The practical skills are difficult to develop through 'chalk and duster' activity in the classroom situation. Accordingly, the 'I' scheme laboratory manual development team designed the practical to focus on the outcomes, rather than the traditional age old practice of conducting practicals to 'verify the theory' (which may become a byproduct along the way).

This laboratory manual is designed to help all stakeholders, especially the students, teachers and instructors to develop in the student the pre-determined outcomes. It is expected from each student that at least a day in advance, they have to thoroughly read through the concerned practical procedure that they will do the next day and understand the minimum theoretical background associated with the practical. Every practical in this manual begins by identifying the competency, industry relevant skills, course outcomes and practical outcomes which serve as a key focal point for doing the practical. The students will then become aware about the skills they will achieve through procedure shown there and necessary precautions to be taken, which will help them to apply in solving real-world problems in their professional life.

This manual also provides guidelines to teachers and instructors to effectively facilitate student-centered lab activities through each practical exercise by arranging and managing necessary resources in order that the students follow the procedures and precautions systematically ensuring the achievement of outcomes in the students.

In the present scenario most of the electronic equipment like computers, mobiles, music systems, ATM, automation and control circuits and systems are based on digital circuits which the diploma electronic engineering pass outs have to test them. The knowledge of basic logic gates, combinational and sequential logic circuits using discrete gates as well as digital ICs will enable the students to interpret the working of equipment and maintain them. After completion of the course, students will be able to develop digital circuits based applications.

Although best possible care has been taken to check for errors (if any) in this laboratory manual, perfection may elude us as this is the first edition of this manual. Any errors and suggestions for improvement are solicited and highly welcome

### Programme Outcomes (POs) to be achieved through Practical of this Course:-

- PO1. **Basic knowledge:** Apply knowledge of basic mathematics, sciences and basic engineering to solve the broad-based Electronics and Computer engineering problems.

- PO2. **Discipline knowledge:**. Apply Electronics and Computer engineering knowledge to solve broad-based Electronics and Computers engineering related problems.

- PO3. **Experiments and practice:** Plan to perform experiments and practices to use the results to solve broad-based Electronics and Telecommunication engineering problems.

- PO4. **Engineering tools:** Apply relevant Electronics and Computer technologies and tools with an understanding of the limitations.

- PO5. **The engineer and society:** Assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to practice in field of Electronics and Telecommunication engineering.

- PO6. **Environment and sustainability:** Apply Electronics and Telecommunication engineering solutions also for sustainable development practices in societal and environmental contexts.

- PO7. **Ethics:** Apply ethical principles for commitment to professional ethics, responsibilities and norms of the practice also in the field of Electronics and Telecommunication engineering.

- PO8. **Individual and team work:** Function effectively as a leader and team member in diverse/ multidisciplinary teams.

- PO9. Communication: Communicate effectively in oral and written form.

- PO10. **Life-long learning:** Engage in independent and life-long learning activities in the context of technological changes also in the Electronics and Telecommunication engineering and allied industry.

#### **Practical- Course Outcome matrix**

#### **Course Outcomes (COs)**

- a Use number system and codes for interpreting working of digital system.

- b Use Boolean expressions to realize logic circuits.

- c Build simple combinational circuits.

- d Build simple sequential circuits.

- e Test data converters and PLDs in digital electronics systems.

| S. No.  | 11000001 0 0000000                                                                            |   | CO | CO | CO | CO |

|---------|-----------------------------------------------------------------------------------------------|---|----|----|----|----|

| 5. 110. |                                                                                               |   | b  | c  | d  | e. |

| 1       | Test the functionality of specified logic gates using breadboard. (IC 7404, 7408, 7432, 7486) | - | √  | -  | _  | _  |

| 2       | Test the functionality of NAND and NOR gate using breadboard (IC 7400 and 7402)               | _ | √  | _  | _  | -  |

| 3       | Construct AND, OR, NOT gates using universal gates.                                           | _ | √  | _  | _  | -  |

| 4       | Build the logic circuit on breadboard to check the De Morgan's theorems.                      | _ | √  | _  | _  | -  |

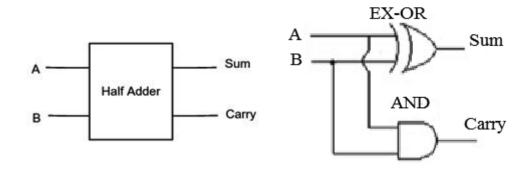

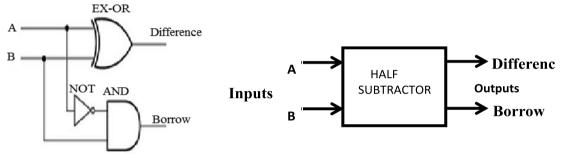

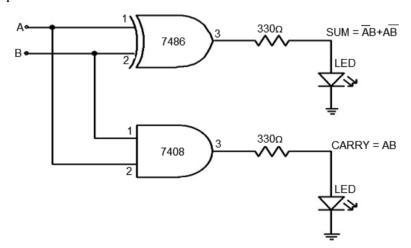

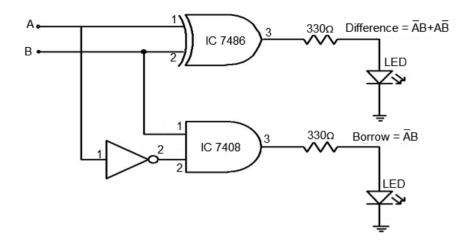

| 5       | Design Half adder and Half subtractor using Boolean expressions.                              | _ | _  | √  | _  | -  |

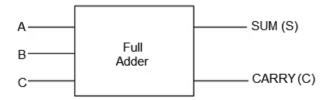

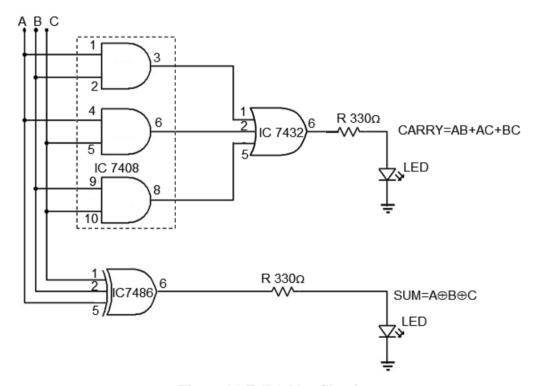

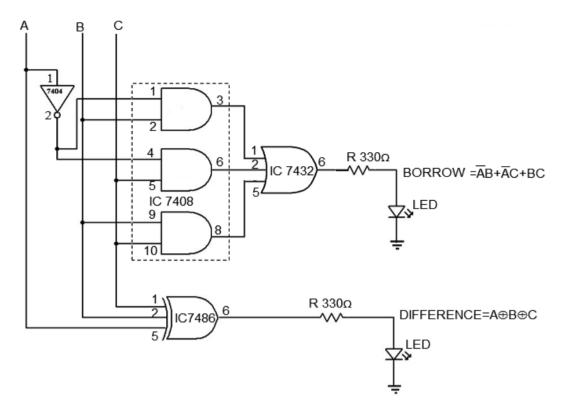

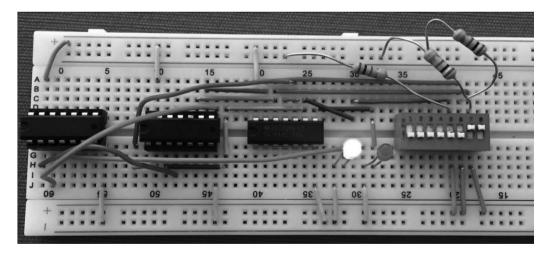

| 6       | Design Full adder and full subtractor.                                                        | _ | _  | √  | _  | -  |

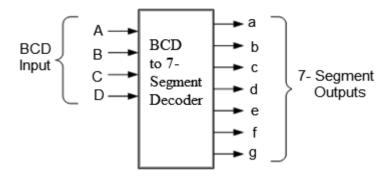

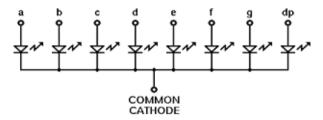

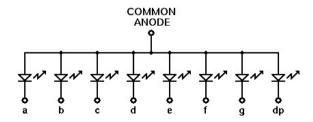

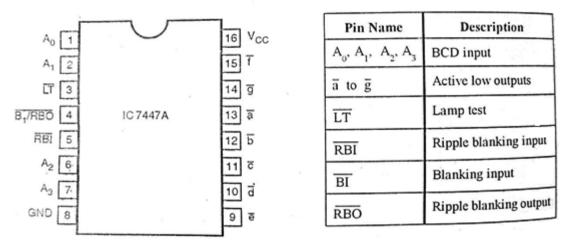

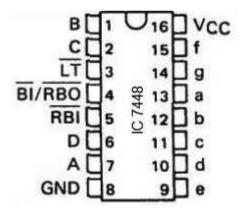

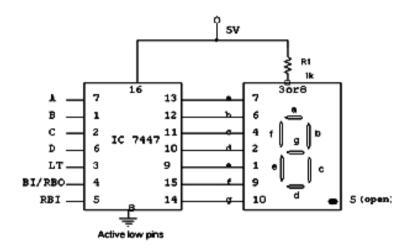

| 7       | Construct and test BCD to 7 segment decoder using IC 7447/ 7448.                              | _ | _  | √  | _  | -  |

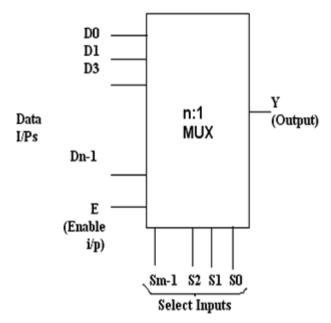

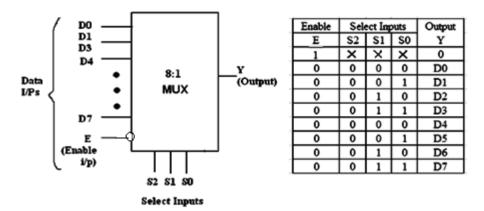

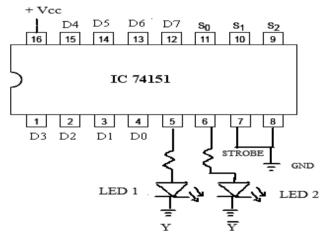

| 8       | Build / test function of MUX 74151/74150/any other equivalent.                                | _ | _  | √  | _  | -  |

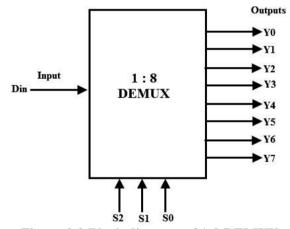

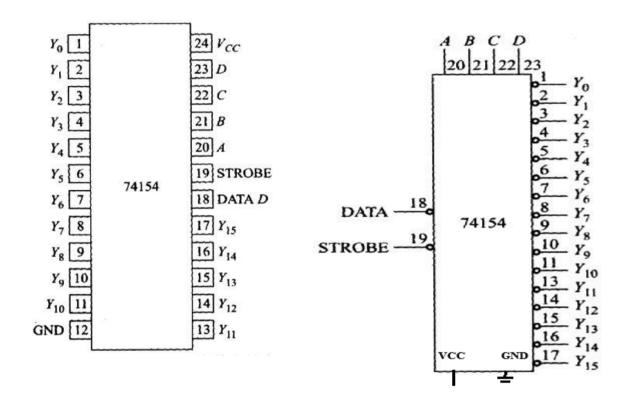

| 9       | Build / test function of DEMUX74155/74154/ any other equivalent.                              | _ | _  | √  | _  | -  |

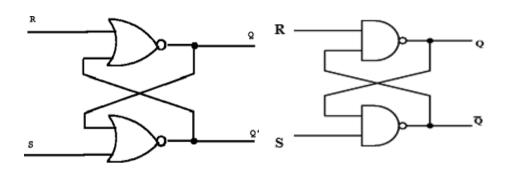

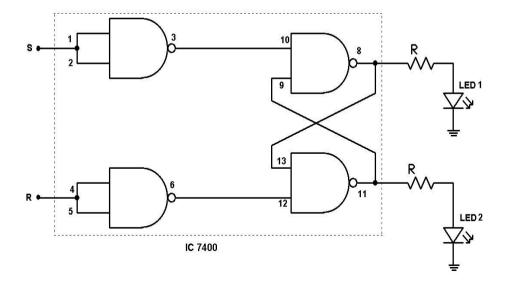

| 10      | Build / test function of RS flip flop using NAND Gate.                                        | _ | _  | _  | √  | -  |

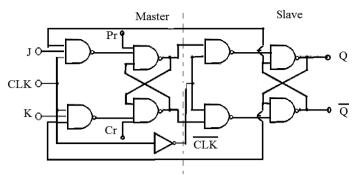

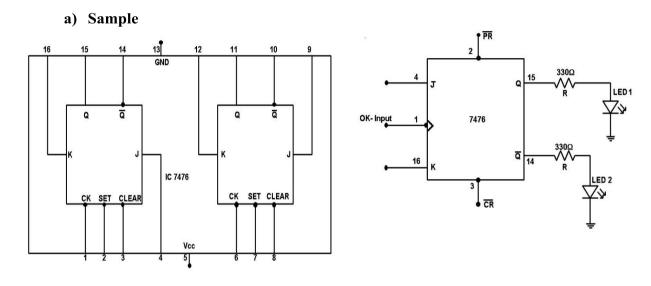

| 11      | Build / test function of MS JK flip flop using 7476.                                          | _ | _  | _  | √  | -  |

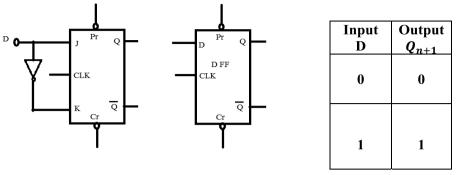

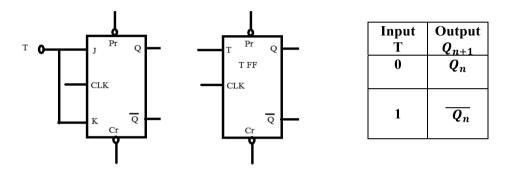

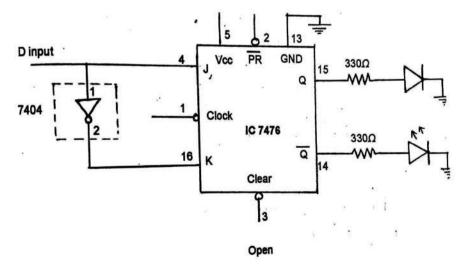

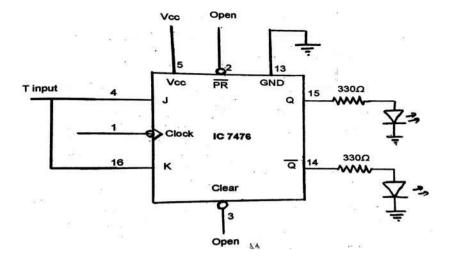

| 12      | Use IC 7476 to construct and test the functionality of D and T flip flop.                     | _ | _  | _  | √  | -  |

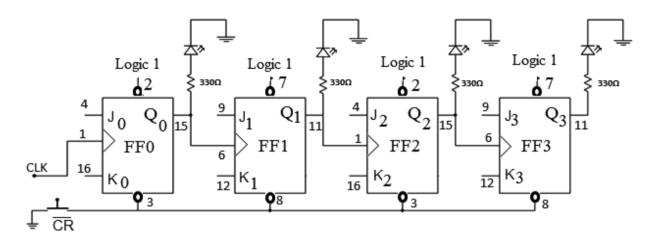

| 13      | Build/Testt 4 bit ripple counter using 7476.                                                  | - | _  | -  | √  | _  |

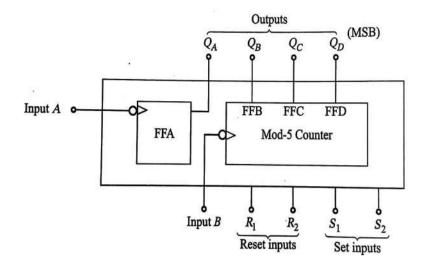

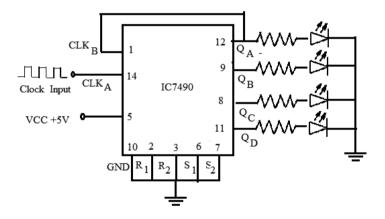

| 14      | Use IC 7490 to construct decade counter (MOD-10).                                             | - | _  | -  | √  | _  |

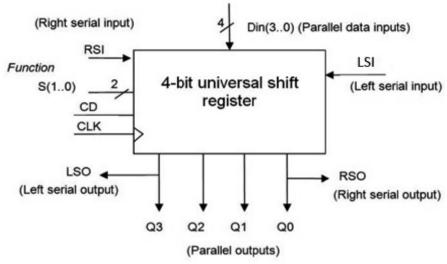

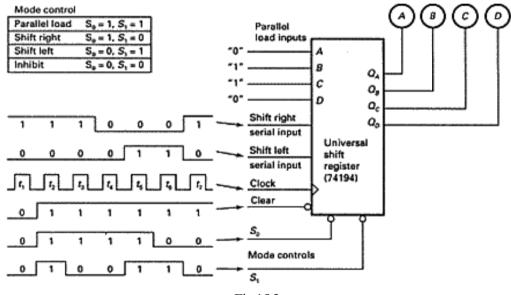

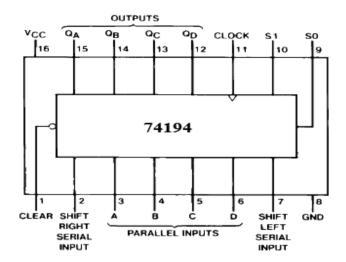

| 15      | Build/test 4 bit universal shift register.                                                    | - | _  | -  | √  | -  |

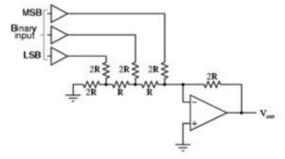

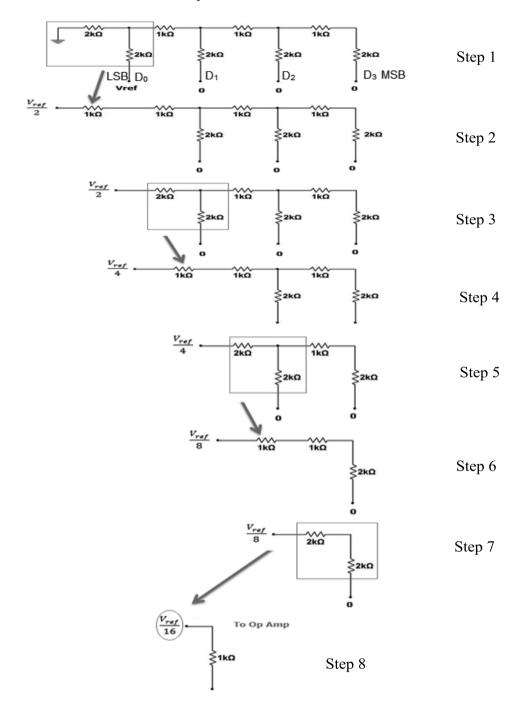

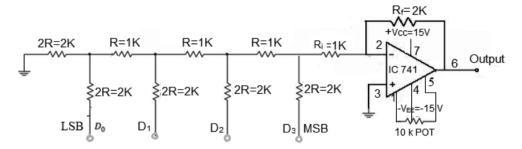

| 16      | Build R-2R resistive network on breadboard to convert given digital data into analog.         | - | -  | -  | -  | V  |

#### **List of Industry Relevant Skills**

The following industry relevant skills of the competency 'Build/ test digital logic circuits consist of digital ICs.' are expected to be developed in you by undertaking the practicals of this laboratory manual.

- 1. Identify the electronic IC / component.

- 2. Identify pin configuration for gates.

- 3. Test electronic IC / component.

- 4. Select the electronic component of proper value as per the requirement.

- 5. Select the appropriate range and instrument.

- 6. Mount the electronic component on breadboard as per circuit diagram.

- 7. Test the circuit for the given application.

- 8. Implement given Boolean equation using logic gates.

- 9. Use appropriate digital circuit.

- 10. Compare the observed output with the expected output.

#### **Guidelines to Teachers**

- 1. Teacher should provide the guideline with demonstration of practical to the students with all features.

- 2. Teacher shall explain prior concepts to the students before starting of each practical

- 3. Involve students in performance of each experiment.

- 4. Teacher should ensure that the respective skills and competencies are developed in the students after the completion of the practical exercise.

- 5. Teachers should give opportunity to students for hands on experience after the demonstration.

- 6. Teacher is expected to share the skills and competencies to be developed in the students.

- 7. Teacher may provide additional knowledge and skills to the students even though not covered in the manual but are expected the students by the industry.

- 8. Finally give practical assignment and assess the performance of students based on task assigned to check whether it is as per the instructions.

- 9. If practical is in two parts -Part I and Part II it should be conducted in two weeks.

- 10. Teacher is expected to refer complete curriculum document and follow guidelines for implementation

- 11. For difficult practicals if required, teacher could provide the demonstration of the practical emphasizing of the skills which the student should achieve.

- 12. Teachers should give opportunity to students for hands-on after the demonstration.

- 13. Teachers should give opportunity to students for hands-on after the demonstration.

- 14. Assess the skill achievement of the students and COs of each unit

#### **Instructions for Students**

- 1. Listen carefully the lecture given by teacher about course, curriculum, learning structure, skills to be developed.

- 2. Organize the work in the group and make record of all observations.

- 3. Students shall develop maintenance skill as expected by industries.

- 4. Student shall attempt to develop related hand-on skills and gain confidence.

- 5. Student shall develop the habits of evolving more ideas, innovations, skills etc. those included in scope of manual

- 6. Student shall refer technical magazines, IS codes and data books.

- 7. Student should develop habit to submit the practical on date and time.

- 8. Student should well prepare while submitting write-up of exercise.

# Content Page List of Practicals and Progressive Assessment Sheet

| S.<br>No | Title of Practical                                               | Page<br>No. | Date of perfor mance | Date of<br>submi<br>ssion | Assess<br>ment<br>marks(25) | Dated<br>sign. of<br>teacher | Rema<br>rks(if<br>any) |

|----------|------------------------------------------------------------------|-------------|----------------------|---------------------------|-----------------------------|------------------------------|------------------------|

| 1.       | Test the Functionality of logic gates                            | 1           |                      |                           |                             |                              |                        |

| 2.       | Test the Functionality of Universal logic gates                  | 8           |                      |                           |                             |                              |                        |

| 3.       | Construct basic gates using universal gates.                     | 15          |                      |                           |                             |                              |                        |

| 4.       | Verify De Morgan's Theorems.                                     | 23          |                      |                           |                             |                              |                        |

| 5.       | Design Half adder and Half Sutractor using Boolean expressions.  | 30          |                      |                           |                             |                              |                        |

| 6.       | Design Full adder and full subtractor.                           | 37          |                      |                           |                             |                              |                        |

| 7.       | Construct and test BCD to 7 segment decoder using IC 7447/ 7448. | 45          |                      |                           |                             |                              |                        |

| 8.       | Verify operation of Multiplexer (MUX).                           | 55          |                      |                           |                             |                              |                        |

| 9.       | Functionality of Demultiplexer(DEMUX).                           | 62          |                      |                           |                             |                              |                        |

| 10.      | Test functionality of RS flip flop using NAND gate.              | 69          |                      |                           |                             |                              |                        |

| 11.      | Test functionality of MS JK flip flop.                           | 75          |                      |                           |                             |                              |                        |

| 12.      | Test the functionality of D and T flip flop.                     | 81          |                      |                           |                             |                              |                        |

| 13.      | 4 bit ripple counter                                             | 87          |                      |                           |                             |                              |                        |

| 14.      | Decade counter using IC 7490.                                    | 94          |                      |                           |                             |                              |                        |

| 15.      | 4 bit universal shift register.                                  | 100         |                      |                           |                             |                              |                        |

| 16.      | R-2R resistive network.                                          | 106         |                      |                           |                             |                              |                        |

|          | Total                                                            |             |                      |                           |                             |                              |                        |

• To be transferred to Proforma of CIAAN-2017

#### Practical No.1: Test the functionality of logic gates.

#### I Practical Significance

Logic gates are the basic building block of all type of digital systems. Digital gates are used in all digital circuits such as switches, memories, microprocessor, and embedded systems. Knowledge of functions of logic gates will help the students to build the digital circuits.

#### II Relevant Program Outcomes (POs)

- **Basic knowledge:** Apply knowledge of basic mathematics, sciences and basic engineering to solve the broad-based Electronics and Computer engineering problems.

- **Discipline knowledge:** Apply Electronics and Computer knowledge to solve broadbased electronics and telecommunication engineering related problems.

- Experiments and practice: Plan to perform experiments and practices to use the results to solve broad-based Electronics and Computer engineering problems.

- **Engineering tools:** Apply relevant Electronics and Computer technologies and tools with an understanding of the limitations.

#### **III** Competency and Practical Skills

This practical is expected to develop the following skills for the industry-identified competency: 'Build/ test digital logic circuits using digital ICs.'

- 1. Verify voltage level for logic 0 and 1.

- 2. Identify pin configuration of logic gate IC's.

- 3. Test the functionality of the logic gates.

#### IV Relevant Course Outcome(s)

• Use Boolean expressions to realize logic circuits.

#### V Practical Outcome

• Test the functionality of specified logic gates using breadboard. (IC 7404, 7408,7432, 7486)

#### VI Relevant Affective domain related Outcome(s)

- Handle IC and equipment carefully.

- Follow safe practices.

#### VII Minimum Theoretical Background

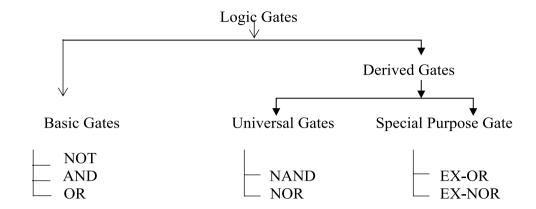

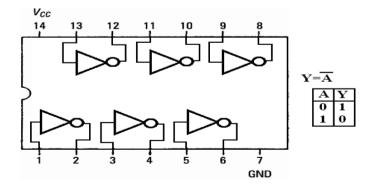

A logic gate is an electronic circuit which makes logical decisions. It has only one output and one or many inputs. The output signal appears for certain combinations of input signals. Logic gates are the basic building blocks of all digital systems. These gates are AND, OR, NOT, NAND, NOR, EXOR and EXNOR gates. The basic operations are described below with the help of truth tables.

In digital logic design only two voltage levels or states are applied as input, and these states are generally referred to as Logic "1" and Logic "0", High and Low, or True and False. These two states are represented in truth tables as binary digits "1" and "0" respectively.

#### **Classification of Logic Gates:-**

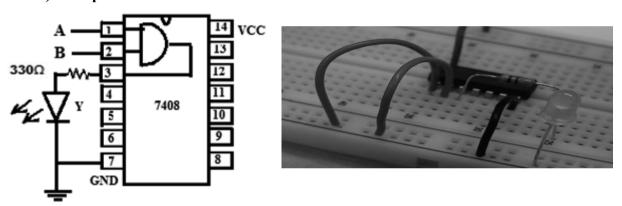

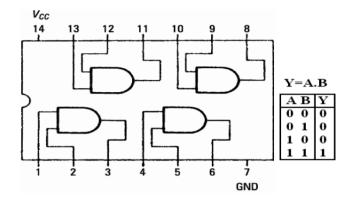

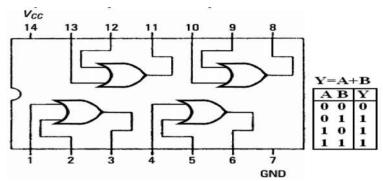

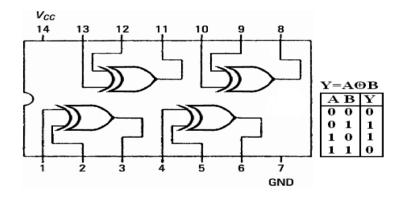

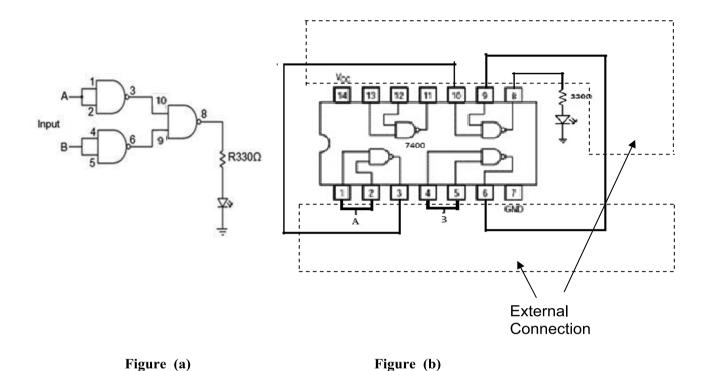

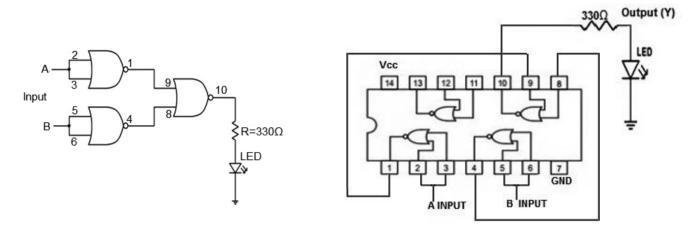

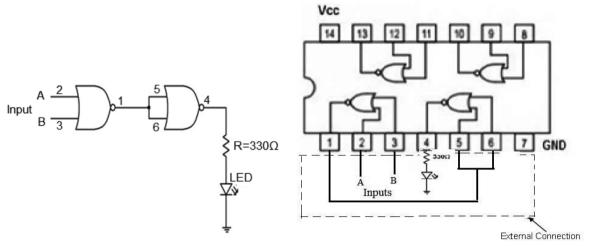

#### VIII Practical Circuit diagram

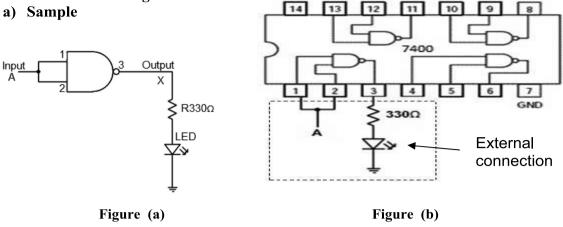

#### a) Sample

Figure 1.1: Sample Circuit

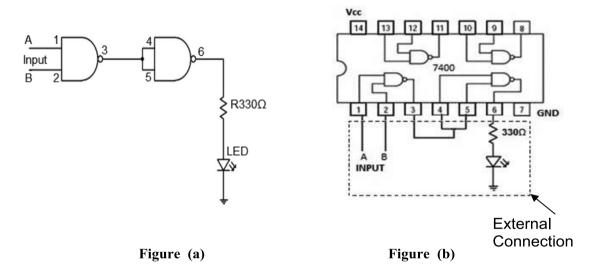

Figure 1.2 NOT Gate IC 7404 and truth table

Figure 1.3 AND gate IC 7408and truth table

Figure 1.4. OR Gate IC 7432and truth table

Figure 1.5 EX-OR Gate IC 7486and truth table

#### b) Actual Circuit used in laboratory

#### c) Actual Experimental set up used in laboratory

#### IX Resources Required

| S.<br>No. | Instrument /Components | Specification                                                                    | Quantity       | Remarks |

|-----------|------------------------|----------------------------------------------------------------------------------|----------------|---------|

| 1.        | Digital<br>Multimeter  | Digital Multimeter: 3 1/2 digit display.                                         | 2              |         |

| 2         | Digital IC<br>Tester   | Tests a wide range of Digital IC's such as 74 Series, 40/45 Series of CMOS IC's. | 1              |         |

| 3         | DC power supply        | +5 V Fixed power supply                                                          | 1              |         |

| 4         | Breadboard             | 5.5cm X 17 cm                                                                    | 1              |         |

| 5         | IC                     | 7486, 7404, 7432, 7408                                                           | 1 Each         |         |

| 6         | LED                    | Red /Yellow color 5 mm                                                           | 1              |         |

| 7         | Connecting wires       | Single strand 0.6 mm<br>Teflon coating                                           | As required    |         |

| 8         | Resistor               | $1.1 \text{ K}\Omega \text{ or } 330\Omega$                                      | As<br>required |         |

#### **X** Precautions to be followed

Do not switch ON the power supply unless you have checked the circuit connections as per the circuit diagram.

#### XI Procedure

- 1. Identify pin configuration of logic gate IC (7408) and test with digital IC Tester.

- 2. Make the connections as per figure 1.1 on breadboard and give supply voltage to relevant pin as per logic level.

- 3. Observe the LED (on or off) for each combination of input as per truth table.

- 4. Verify the truth table.

- 5. Repeat the process for IC 7404, 7432, 7486.

#### XII Resources used (with major specifications)

**Observations and Calculations**

| S. No. | Instrument /Components | Specification | Quantity |

|--------|------------------------|---------------|----------|

| 1.     |                        |               |          |

| 2.     |                        |               |          |

| 3.     |                        |               |          |

| 4.     |                        |               |          |

| 5.     |                        |               |          |

| XIII | Actual procedure followed (Use blank sheet provided if space not sufficient) |

|------|------------------------------------------------------------------------------|

|      |                                                                              |

|      |                                                                              |

| XIV  | Precautions followed (Use blank sheet provided if space not sufficient)      |

|      |                                                                              |

|      |                                                                              |

#### **Table 1.1: Observation table**

| Inp   | uts   | 7404 (                    | NOT)                 | <b>7408</b> (A            | AND)              | 7432(OR)                  |                   | 7486(EX-OR)               |                   |

|-------|-------|---------------------------|----------------------|---------------------------|-------------------|---------------------------|-------------------|---------------------------|-------------------|

| A     | В     | LED<br>Status<br>(ON/OFF) | Output<br>voltage(v) | LED<br>Status<br>(ON/OFF) | Output<br>voltage | LED<br>Status<br>(ON/OFF) | Output<br>voltage | LED<br>Status<br>(ON/OFF) | Output<br>voltage |

| 0(0V) | 0(0V) |                           |                      |                           |                   |                           |                   |                           |                   |

| 0(0V) | 1(5V) |                           |                      |                           |                   |                           |                   |                           |                   |

| 1(5V) | 0(0V) |                           |                      |                           |                   |                           |                   |                           |                   |

| 1(5V) | 1(5V) |                           |                      |                           |                   |                           |                   |                           |                   |

| XVI  | Results                                                                                             |

|------|-----------------------------------------------------------------------------------------------------|

|      |                                                                                                     |

| XVII | Interpretation of results (Give meaning of the above obtained results)                              |

|      |                                                                                                     |

|      | Conclusions & Recommendation (Actions/decisions to be taken based on the interpretation of results) |

|      |                                                                                                     |

|      |                                                                                                     |

#### **XIX** Practical Related Questions

Note: Below given are few sample questions for reference. Teachers must design more such questions so as to ensure the achievement of identified CO.

- 1. Write down voltage at logic level 0 and 1.

- 2. List the function of pin 7,14of IC 7432.

- 3. State the effect if pin number 14 is connected to ground and pin number 7 is connected to VCC?

- 4. List numbers of NOT gates are available in IC 7404.

- 5. List the name of manufacturers of Digital IC used in your lab.

- 6. State the need for the resister connected in series with LED. Write down the value of resister.

- 7. State the significance of LS of IC number 74LS00.

| [Space for answer] |

|--------------------|

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

| igital Techniques (22320) |

|---------------------------|

|                           |

|                           |

|                           |

|                           |

|                           |

|                           |

|                           |

|                           |

#### XX References / Suggestions for further reading

- 1. http://www.electronics-tutorials.ws/logic/logic 1.html

- 2. https://www.youtube.com/watch?v=AT GjUjNFpo

- 3. https://www.youtube.com/watch?v=EBlgoycFNJ8

- 4. https://www.youtube.com/watch?v=LBuLmC0chyQ

- 5. https://www.youtube.com/watch?v=WGYEpZQnRE8

- 6. http://www.ti.com/lit/ds/symlink/sn74ls00.pdf

#### XXI Assessment Scheme

|    | Weightage                              |      |  |  |  |

|----|----------------------------------------|------|--|--|--|

|    | Process related:15 Marks               |      |  |  |  |

| 1  | Verification of voltage                | 10 % |  |  |  |

| 2  | Handling of the components/IC          | 10 % |  |  |  |

| 3  | Identification of component/IC         | 10 % |  |  |  |

| 4  | Mounting of IC on Breadboard           | 20 % |  |  |  |

| 5  | Working in team                        | 10 % |  |  |  |

|    | Product related:10 Marks               | 40%  |  |  |  |

| 6  | Result                                 | 10 % |  |  |  |

| 7  | Interpretation of result               | 05 % |  |  |  |

| 8  | Conclusions                            | 05 % |  |  |  |

| 9  | Answers to Practical related questions | 15 % |  |  |  |

| 10 | Submitting the journal in time         | 05%  |  |  |  |

|    | Total (25 Marks) 100 %                 |      |  |  |  |

| 1. |  |

|----|--|

| 2. |  |

| 3. |  |

| 4. |  |

| Ma                     | arks Obtained          | Dated signature of<br>Teacher |  |

|------------------------|------------------------|-------------------------------|--|

| Process<br>Related(15) | Product<br>Related(10) | <b>Total</b> (25)             |  |

|                        |                        |                               |  |

#### Practical No.2: Test the functionality of universal logic gates.

#### I Practical Significance

A universal gate is a gate which can implement any Boolean function without need to use any other gate type. In practice, this is advantageous since NAND and NOR gates are economical and easier to fabricate and are the basic gates used in all IC digital logic families.

#### II Relevant Program Outcomes (POs)

- **Basic knowledge:** Apply knowledge of basic mathematics, sciences and basic engineering to solve the broad-based Electronics and Computer engineering problems

- **Discipline knowledge:** Apply Electronics and Computer knowledge to solve broad-based Electronics and Computer engineering related problems.

- **Experiments and practice:** Plan to perform experiments and practices to use the results to solve broad-based Electronics and Computer engineering problems.

- **Engineering tools:** Apply relevant Electronics and Computer technologies and tools with an understanding of the limitations.

#### III Competency and Practical Skills

This practical is expected to develop the following skills for the industry-identified competency: 'Build/ test digital logic circuits consist of digital ICs.'

- 1. Verify voltage level for logic 0 and 1.

- 2. Identify pin configuration of logic gate IC's.

- 3. Test the functionality of the logic gates.

#### IV Relevant Course Outcome(s)

• Use Boolean expressions to realize logic circuits.

#### V Practical Outcome

• Test the functionality of NAND and NOR gate using breadboard (IC 7400 and 7402).

#### VI Relevant Affective domain related Outcome(s)

- Handle IC and equipment carefully.

- Follow safe practices.

#### VII Minimum Theoretical Background

OR,AND and NOT gates are the three basic logic gates as they together can be used to construct the logic circuit for any given Boolean expression. NOR and NAND gates have the property that they individually can be used to implement logic circuit corresponding to any given Boolean expression.

The NAND and NOR gates are known as universal gates.

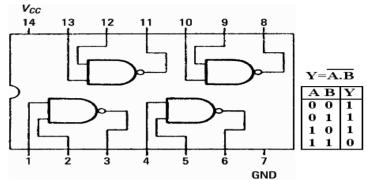

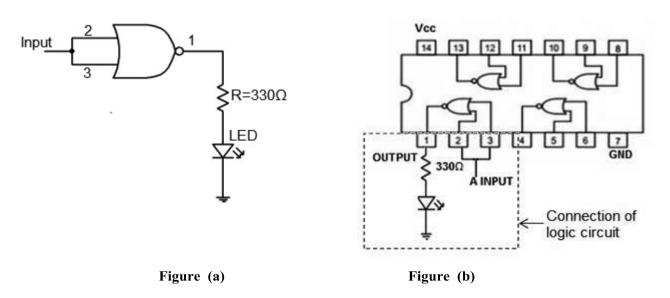

#### VIII Practical Circuit diagram

#### a) Sample

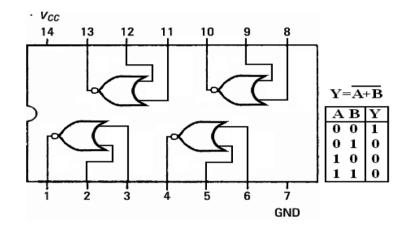

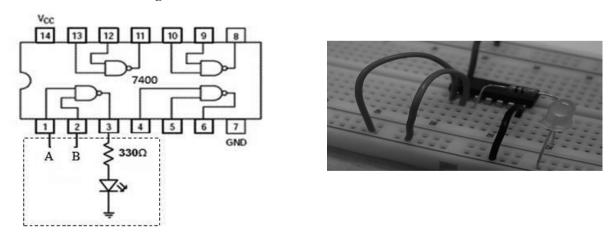

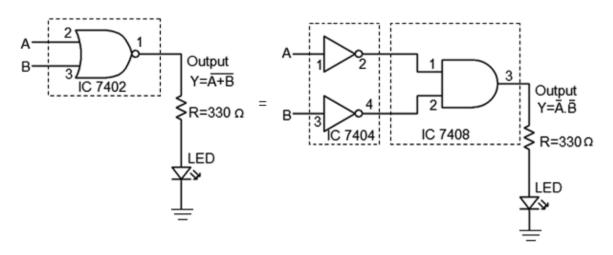

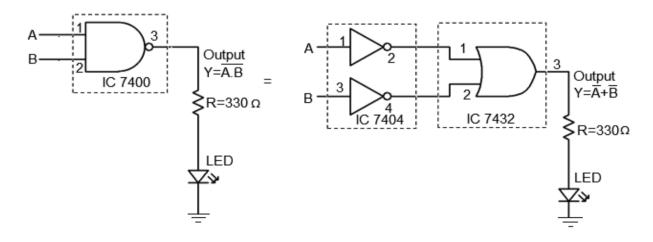

Figure 2.1.NAND Gate IC 7400 and Truth table

Figure 2.2.NOR Gate IC 7402 and Truth table

Figure 2.3: Sample Circuit

| <b>b</b> ) | ) | Actual | Circuit | used in | laboratory |

|------------|---|--------|---------|---------|------------|

|            |   |        |         |         |            |

c) Actual Experimental set up used in laboratory

#### IX Resources Required

| S.<br>No. | Instrument<br>/Component<br>s | Specification                                                                             | Quantity    | Remarks |

|-----------|-------------------------------|-------------------------------------------------------------------------------------------|-------------|---------|

| 1.        | Digital<br>Multimeter         | Digital Multimeter: 3 1/2 digit display.                                                  | 2           |         |

| 2.        | Digital IC<br>Tester          | Tests a wide range of<br>Digital IC's such as 74<br>Series, 40/45 Series of<br>CMOS IC's. | 1           |         |

| 3.        | DC power supply               | +5 V Fixed power supply                                                                   | 1           |         |

| 4.        | Breadboard                    | 5.5cm X 17 cm                                                                             | 1           |         |

| 5.        | IC                            | 7400, 7402                                                                                | 1 Each      |         |

| 6.        | LED                           | Red /Yellow color 5 mm                                                                    | 1           |         |

| 7.        | Connecting wires              | Single strand 0.6 mm Teflon coating                                                       | As required |         |

| 8         | Resistor                      | $1$ K $\Omega$ or $330$ $\Omega$                                                          | As required |         |

#### **X** Precautions to be Followed

Do not switch ON the power supply unless you have checked the circuit connections as per the circuit diagram.

#### XI Procedure

- 1. Identify pin configuration of logic gate IC (7400) and test with digital IC tester.

- 2. Make the connections as per figure 2.3 on breadboard and give supply voltage to relevant pin as per logic level.

- 3. Observe the LED (on or off) for each combination of input as per truth table.

- 4. Verify the truth table.

- 5. Repeat the process for IC 7402.

#### XII Resources used (with major specifications)

| S. No. | Instrument /Components | Specification | Quantity |

|--------|------------------------|---------------|----------|

| 1.     |                        |               |          |

| 2.     |                        |               |          |

| 3.     |                        |               |          |

| 4.     |                        |               |          |

| 5.     |                        |               |          |

| XIII | Actual procedure followed (Use blank sheet provided if space not sufficient) |

|------|------------------------------------------------------------------------------|

|      |                                                                              |

|      |                                                                              |

|      |                                                                              |

|      |                                                                              |

|      |                                                                              |

| Table 2.1    Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | IV               | Preca                     | autions foll                                                             | <b>owed</b> (Use blank                                                                                                         | sheet provided if                                                                                  | space not suffic                                               | cient)         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------|

| Table 2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                           | • • • • • • • • • • • • • • • • • • • •                                  |                                                                                                                                |                                                                                                    |                                                                |                |

| Table 2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                           |                                                                          |                                                                                                                                |                                                                                                    |                                                                |                |

| Table 2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                           | • • • • • • • • • • • • • • • • • • • •                                  |                                                                                                                                |                                                                                                    |                                                                |                |

| Table 2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  | •••••                     | •••••                                                                    | •••••                                                                                                                          |                                                                                                    | •••••                                                          |                |

| A B LED Status (ON/OFF) Output voltage LED Status (ON/OFF)  O(0V) 0(0V) 1(5V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V                | Obse                      | rvations ar                                                              | d Calculations.                                                                                                                | Table 2.1                                                                                          |                                                                |                |

| A B LED Status (ON/OFF) Output voltage LED Status (ON/OFF)  O(0V) 0(0V) 1(5V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  | Inp                       | uts                                                                      | 7400 (                                                                                                                         | (NAND)                                                                                             | 7402                                                           | 2(NOR)         |

| Comparison of the comparison | A                |                           | В                                                                        |                                                                                                                                | Output voltage                                                                                     |                                                                | Output voltage |

| TI Results  TI Conclusions & Recommendation (Actions/decisions to be taken based on the interpretation of results)  X Practical Related Questions  Note: Below given are few sample questions for reference. Teachers must design more such questions so as to ensure the achievement of identified CO.  1. List the function of pin 7 and 14 of IC 7400.  2. Write down name of manufacturer of Digital IC 7400, 7402 used in practical.  3. Suggest another IC used as NAND, AND, NOR Gate.  4. Write the IC no. which has three input NAND &NOR gate.  [Space for answer]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0(07             | V)                        | 0(0V)                                                                    |                                                                                                                                |                                                                                                    |                                                                |                |

| TI Results  TI Interpretation of results (Give meaning of the above obtained results)  TII Conclusions & Recommendation (Actions/decisions to be taken based on the interpretation of results)  X Practical Related Questions  Note: Below given are few sample questions for reference. Teachers must design more such questions so as to ensure the achievement of identified CO.  1. List the function of pin 7 and 14 of IC 7400.  2. Write down name of manufacturer of Digital IC 7400, 7402 used in practical.  3. Suggest another IC used as NAND, AND, NOR Gate.  4. Write the IC no. which has three input NAND &NOR gate.  [Space for answer]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0(0              | V)                        | 1(5V)                                                                    |                                                                                                                                |                                                                                                    |                                                                |                |

| TI Interpretation of results (Give meaning of the above obtained results)  TII Conclusions & Recommendation (Actions/decisions to be taken based on the interpretation of results)  X Practical Related Questions  Note: Below given are few sample questions for reference. Teachers must design more such questions so as to ensure the achievement of identified CO.  1. List the function of pin 7 and 14 of IC 7400.  2. Write down name of manufacturer of Digital IC 7400, 7402 used in practical.  3. Suggest another IC used as NAND, AND, NOR Gate.  4. Write the IC no. which has three input NAND &NOR gate.  [Space for answer]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1(5 <b>Y</b>     | V)                        | 0(0V)                                                                    |                                                                                                                                |                                                                                                    |                                                                |                |

| TII Interpretation of results (Give meaning of the above obtained results)  TII Conclusions & Recommendation (Actions/decisions to be taken based on the interpretation of results)  X Practical Related Questions  Note: Below given are few sample questions for reference. Teachers must design more such questions so as to ensure the achievement of identified CO.  1. List the function of pin 7 and 14 of IC 7400.  2. Write down name of manufacturer of Digital IC 7400, 7402 used in practical.  3. Suggest another IC used as NAND, AND, NOR Gate.  4. Write the IC no. which has three input NAND &NOR gate.  [Space for answer]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1(5 <sup>v</sup> | V)                        | 1(5V)                                                                    |                                                                                                                                |                                                                                                    |                                                                |                |

| Note: Below given are few sample questions for reference. Teachers must design more such questions so as to ensure the achievement of identified CO.  1. List the function of pin 7 and 14 of IC 7400.  2. Write down name of manufacturer of Digital IC 7400, 7402 used in practical.  3. Suggest another IC used as NAND, AND, NOR Gate.  4. Write the IC no. which has three input NAND &NOR gate.  [Space for answer]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  | Conc                      | lusions & 1                                                              | Recommendation                                                                                                                 |                                                                                                    |                                                                |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | X                | Note: more 1. L 2. W 3. S | Below give<br>such questi<br>ist the funct<br>rite down r<br>uggest anot | en are few sample<br>ons so as to ensu-<br>tion of pin 7 and in<br>name of manufact<br>ther IC used as NA<br>no. which has thr | re the achievement<br>14 of IC 7400.<br>Sturer of Digital IC<br>AND, AND, NOR<br>Stee input NAND & | nt of identified C<br>27400, 7402 use<br>2 Gate.<br>2NOR gate. | CO.            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |                           |                                                                          |                                                                                                                                |                                                                                                    |                                                                |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |                           | •••••                                                                    |                                                                                                                                |                                                                                                    |                                                                |                |

| Digital Techniques (22320) |

|----------------------------|

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

|                            |

| Digita | nai Techniques (22320)                       |  |

|--------|----------------------------------------------|--|

|        |                                              |  |

|        |                                              |  |

|        |                                              |  |

|        |                                              |  |

|        |                                              |  |

|        | References / Suggestions for further reading |  |

- - 1. www.alldatasheet.com/datasheet-pdf

- 2. http://www.electronics-tutorials.ws/logic/logic 1.html

- 3. https://www.youtube.com/watch?v=nDOCqIVUdk4

- 4. https://www.youtube.com/watch?v=146DbuTCzGQ&t=14s